# **Functional Safety Manual**

for Safety Related Systems and SIL 2, SIL 3 Applications according IEC 61508 & IEC 61511 Standards

# G.M. International **D1000 Series**Intrinsically Safe Interface Modules and Switching Power Supply PSD1206, PSD1210

# **Table of Contents**

| 1 | Gene  | eral                                                                                         | 4     |

|---|-------|----------------------------------------------------------------------------------------------|-------|

| 2 | Func  | tional Safety Specifications from EXIDA and TÜV analysis, report according IEC 61508 - IEC 6 | 15116 |

| 3 | Defir | nitions                                                                                      | 10    |

|   | 3.1   | Failure categories                                                                           | 10    |

|   |       | 3.1.1 Failure categories for PSD1206 and PSD1210                                             | 12    |

|   | 3.2   | General Terms                                                                                | 13    |

| 4 | Assu  | ımptions                                                                                     | 14    |

|   | 4.1   | Assumption for PSD1206 and PSD1210                                                           | 15    |

| 5 | Sum   | mary of Data from EXIDA and TÜV analysis                                                     | 16    |

|   | 5.1   | D1010S Isolating Repeater Power Supply, Hart Compatible (Active Input)                       | 16    |

|   | 5.2   | D1010S Isolating Repeater Power Supply, Hart Compatible (Passive Input)                      | 17    |

|   | 5.3   | D1010D Isolating Repeater Power Supply, Hart Compatible (Active Input)                       | 18    |

|   | 5.4   | D1010D Isolating Repeater Power Supply, Hart Compatible (Passive Input)                      | 19    |

|   | 5.5   | D1010S-054 Isolating -5 ÷ +55 mV to 4 ÷ 20 mA Converter                                      | 20    |

|   | 5.6   | D1010S-056 Isolating -5 ÷ +35 mV to 4 ÷ 20 mA Converter                                      | 21    |

|   | 5.7   | D1010S-057 Isolating -5 ÷ +10 mV to 4 ÷ 20 mA Converter                                      | 22    |

|   | 5.8   | D1014S and D1014D Isolating Repeater Power Supplies, Hart Compatible                         | 23    |

|   | 5.9   | D1020S and D1020D Powered Isolating Drivers for I/P, Hart Compatible                         | 24    |

|   | 5.10  | D1021S Powered Isolating Driver for I/P, with Fault Detection and Hart Compatible            | 25    |

|   | 5.11  | D1032D Isolating Switch-Proximity Detector Repeater, Relay Output                            | 26    |

|   | 5.12  | D1032Q Isolating Switch-Proximity Detector Repeater, Relay Output                            | 27    |

|   | 5.13  | D1033D Isolating Switch-Proximity Detector Repeater, Transistor output                       | 28    |

|   | 5.14  | D1033Q Isolating Switch-Proximity Detector Repeater, Transistor output                       | 29    |

|   | 5.15  | D1034S and D1034D Isolating Switch-Proximity Detector Interfaces, mA output                  | 30    |

|   | 5.16  | D1040Q, D1042Q, D1043Q, PSD1001(C) Bus Powered Isolating Drivers for NE loads                | 31    |

|   | 5.17  | D1040Q, D1042Q, D1043Q, PSD1001(C) Loop Powered Isolating Drivers for NE loads               | 31    |

|   | 5.18  | D1044S Bus Powered Digital Relay Output for NE or ND loads                                   | 32    |

|   | 5.19  | D1044S Loop Powered Digital Relay Output for NE or ND loads                                  | 33    |

|   | 5.20  | D1044D Bus Powered (independent channels) Digital Relay Output for NE or ND loads            | 34    |

|   | 5.21  | D1044D Bus Powered (1002 channel architecture) Digital Relay Output for NE or ND loads       | 35    |

|   | 5.22  | D1044D Loop Powered (1002 channel architecture) Digital Relay Output for NE or ND loads      |       |

|   | 5.23  | D1048S Loop Powered Digital Output Driver for NE loads                                       | 37    |

|   |       |                                                                                              |       |

|       | 5.24   | D1049S Bus Powered Digital Output Driver for NE loads                                                                             | 38  |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

|       | 5.25   | D1053S Isolating Analog Signals Converter and Trip Amplifiers (using analog output)                                               | 39  |

|       | 5.26   | D1053S Isolating Analog Signals Converter and Trip Amplifiers (using 2 relay outputs in series)                                   | 40  |

|       |        | D1054S Isolating Repeater Power Supply and Trip Amplifiers, Hart Compatible (using active input and goutput)                      |     |

|       |        | D1054S Isolating Repeater Power Supply and Trip Amplifiers, Hart Compatible (using passive input a g output)                      |     |

|       | 5.29   | D1054S Isolating Repeater Power Supply and Trip Amplifiers, Hart Compatible (using active input and outputs in series)            | d 2 |

|       |        | D1054S Isolating Repeater Power Supply and Trip Amplifiers, Hart Compatible (using passive input a youtputs in series)            |     |

|       |        | D1072S Isolating Temperature Signal Converter, D1073S Isolating Temperature Signal Converter and Amplifiers (using analog output) |     |

|       | 5.32   | D1072D Isolating Temperature Signal Converter (using analog output)                                                               | 46  |

|       | 5.33   | D1073S Isolating Temperature Converter and Trip Amplifiers (using 2 relay outputs in series)                                      | 47  |

|       | 5.34   | D1092S and D1092D Relay Output Modules for NE loads                                                                               | 48  |

|       | 5.35   | D1092S and D1092D Relay Output Modules for ND loads                                                                               | 49  |

|       | 5.36   | D1092S-069 and D1092D-069 Relay Output Modules, NO contact output                                                                 | 50  |

|       | 5.37   | D1092S-069 and D1092D-069 Relay Output Modules, NC contact output                                                                 | 51  |

|       | 5.38   | D1093S Relay Output Module for NE loads, with Line and Load diagnostics                                                           |     |

|       | 5.39   | D1093S Relay Output Module for ND loads, with Line and Load diagnostics                                                           |     |

|       | 5.40   | PSD1206 and PSD1210 Isolated Switching Power Supplies for NE loads, single unit                                                   |     |

|       | 5.41   |                                                                                                                                   |     |

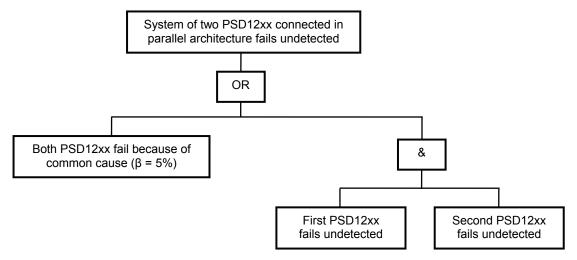

|       |        | PSD1206 and PSD1210 Isolated Switching Power Supplies, 2 units in parallel                                                        |     |

|       | 0      | 5.42.1 NE loads                                                                                                                   |     |

|       |        | 5.42.2 ND loads                                                                                                                   |     |

|       | 5.43   | PSD1206 and PSD1210 Isolated Switching Power Supplies, 3 units in parallel                                                        |     |

|       | 3.43   | 5.43.1 NE loads                                                                                                                   |     |

|       |        | 5.43.2 ND loads                                                                                                                   |     |

|       | E 44   | PSD1206 and PSD1210 Isolated Switching Power Supplies, fail with over voltage condition                                           |     |

| •     |        | s                                                                                                                                 |     |

| 6     |        |                                                                                                                                   |     |

| 7     |        | ible Proof Tests to reveal Dangerous Undetected Failures                                                                          |     |

|       | 7.1    | D1010, D1014                                                                                                                      |     |

|       | 7.2    | D1010S-054, D1010S-056, D1010S-057                                                                                                |     |

|       | 7.3    | D1020, D1021S                                                                                                                     |     |

|       | 7.4    | D1032, D1033                                                                                                                      |     |

|       | 7.5    | D1034                                                                                                                             |     |

|       | 7.6    | D1040, D1042, D1043, PSD1001, PSD1001C                                                                                            |     |

|       | 7.7    | D1044                                                                                                                             |     |

|       | 7.8    | D1049S                                                                                                                            |     |

|       | 7.9    | D1053S and D1054S (using analog output)                                                                                           |     |

|       | 7.10   | D1053S and D1054S (using 2 relay outputs in series)                                                                               |     |

|       | 7.11   | D1072, D1073S (using analog output)                                                                                               | 64  |

|       | 7.12   | D1073S (using 2 relay outputs in series)                                                                                          | 65  |

|       | 7.13   | D1092                                                                                                                             | 66  |

|       | 7.14   | D1092-069                                                                                                                         | 66  |

|       | 7.15   | D1093S                                                                                                                            | 66  |

|       | 7.16   | PSD1206, PSD1210                                                                                                                  | 67  |

|       |        | 7.16.1 Test Setup                                                                                                                 | 67  |

|       |        | 7.16.2 Test of single Power Supply or individual unit of "N" unit in parallel                                                     | 67  |

| ISM00 | 071-13 | D1000 Series Manual for Safety Related System SIL applications Page 2 of                                                          | 71  |

|   | 7.16.3         | Tests required when the unit is used as subsystem of "N" units in parallel | 68 |

|---|----------------|----------------------------------------------------------------------------|----|

| 8 | Impact of Life | etime of Critical Components on Failure Rate                               | 7  |

| 9 | Influence of F | PFDavg calculation on efficiency of Proof Test for a 1oo1 architecture     | 7  |

### 1 General

This Safety Manual summarizes the results of hardware assessment carried out on the following Intrinsically Safe modules:

Repeater – Driver – Interface D1010, D1010S-054 (or -056 or -057), D1014, D1020, D1021S, D1032, D1033, D1034, D1040, D1042, D1043, D1048S, D1049S; Analog Signals Converter and Trip Amplifiers D1053S; Repeater and Trip Amplifiers D1054S; Temperature Signal Converter D1072; Temperature Signal Converter and Trip Amplifiers D1073S; Relay Output modules D1044, D1092, D1092-069, D1093S; Power Supply PSD1001(C), PSD1206, PSD1210.

Table 1: Model – Output channels – Safety Function Table

| Model      | Output channels | Component type | Safety Function                                                           |  |  |

|------------|-----------------|----------------|---------------------------------------------------------------------------|--|--|

| D1010S     | 1               | Α              | Isolating Repeater Power Supply, HART compatible                          |  |  |

| D1010D     | 2               | Α              | Isolating Repeater Power Supply, HART compatible                          |  |  |

| D1010S-054 | 1               | Α              | Isolating -5 ÷ +55 mV to 4 ÷ 20 mA Converter                              |  |  |

| D1010S-056 | 1               | Α              | Isolating -5 ÷ +35 mV to 4 ÷ 20 mA Converter                              |  |  |

| D1010S-057 | 1               | Α              | Isolating -5 ÷ +10 mV to 4 ÷ 20 mA Converter                              |  |  |

| D1014S     | 1               | Α              | Isolating Repeater Power Supply, HART compatible                          |  |  |

| D1014D     | 2               | Α              | Isolating Repeater Power Supply, HART compatible                          |  |  |

| D1020S     | 1               | Α              | Powered Isolating Valve Driver, HART compatible                           |  |  |

| D1020D     | 2               | Α              | Powered Isolating Valve Driver, HART compatible                           |  |  |

| D1021S     | 1               | Α              | Powered Isolating Valve Driver with Fault Detection, HART compatible      |  |  |

| D1032D     | 2               | Α              | Isolating Switch-Proximity Detector Repeater, Relay output                |  |  |

| D1032Q     | 4               | Α              | Isolating Switch-Proximity Detector Repeater, Relay output                |  |  |

| D1033D     | 2               | Α              | Isolating Switch-Proximity Detector Repeater, O.C. Transistor output      |  |  |

| D1033Q     | 4               | Α              | Isolating Switch-Proximity Detector Repeater, O.C. Transistor output      |  |  |

| D1034S     | 1               | Α              | Isolating Switch-Proximity Detector Interface, mA output                  |  |  |

| D1034D     | 2               | Α              | Isolating Switch-Proximity Detector Interface, mA output                  |  |  |

| D1040Q     | 4               | В              | Loop / Bus Powered Isolating Driver for NE loads, 22mA at 13.2V (per ch.) |  |  |

| D1042Q     | 4               | В              | Loop / Bus Powered Isolating Driver for NE loads, 22mA at 14.5V (per ch.) |  |  |

| D1043Q     | 4               | В              | Loop / Bus Powered Isolating Driver for NE loads, 22mA at 9.8V (per ch.)  |  |  |

| D1044S     | 1               | Α              | Loop / Bus Powered Digital Relay Output for NE or ND loads                |  |  |

| D1044D     | 2               | Α              | Loop / Bus Powered Digital Relay Output for NE or ND loads                |  |  |

| D1048S     | 1               | Α              | Loop Powered Digital Output Driver for NE loads                           |  |  |

| D1049S     | 1               | Α              | Bus Powered Digital Output Driver for NE loads                            |  |  |

| D1053S     | 1               | В              | Isolating Analog Signals Converter and Trip Amplifiers                    |  |  |

| D1054S     | 1               | В              | Isolating Repeater Power Supply and Trip Amplifiers, HART compatible      |  |  |

| D1072S     | 1               | В              | Isolating Temperature Signal Converter, Fully Programmable                |  |  |

| D1072D     | 2               | В              | Isolating Temperature Signal Converter, Fully Programmable                |  |  |

| D1073S     | 1               | В              | Isolating Temperature Converter and Trip Amplifiers, Fully Programmable   |  |  |

| D1092S     | 1               | Α              | Relay Output Module for NE or ND loads                                    |  |  |

| D1092D     | 2               | Α              | Relay Output Module for NE or ND loads                                    |  |  |

| D1092S-069 | 1               | Α              | NE Relay Output Module with NO and NC contact outputs                     |  |  |

| D1092D-069 | 2               | Α              | NE Relay Output Module with NO and NC contact outputs                     |  |  |

| D1093S     | 1               | Α              | Relay Output Module for NE or ND loads, with Line and Load diagnostics    |  |  |

| PSD1001    | 4               | В              | Isolating Power Supply 20 mA at 15 V (per channel)                        |  |  |

| PSD1001C   | 1               | В              | Isolating Power Supply 100 mA at 13.5 V                                   |  |  |

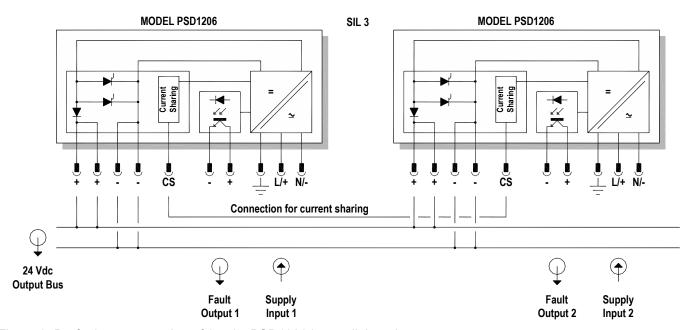

| PSD1206    | 1               | Α              | Isolated Switching Power Supply 6 A at 24 Vdc                             |  |  |

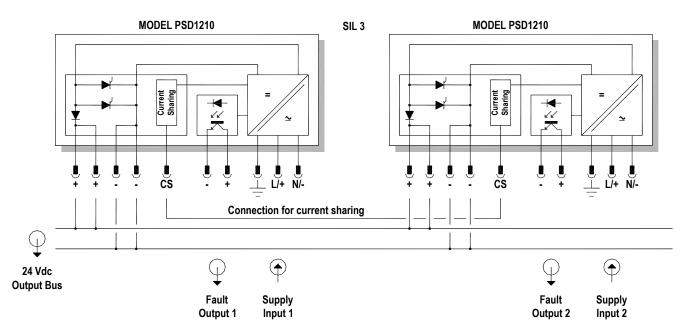

| PSD1210    | 1               | Α              | Isolated Switching Power Supply 10 A at 24 Vdc                            |  |  |

|            |                 |                |                                                                           |  |  |

# GINTERNATIONAL TECHNOLOGY FOR SAFETY

#### D1000 Series Manual for Safety Related System SIL applications

The failure rates used in this analysis are the basic failure rates from the Siemens standard SN 29500. The failure modes distributions used in this analysis are considered according to RAC FMD-91/97.

According the table 2 of IEC 61508-1, the average PFD for systems operating in low demand mode has to be from  $\geq 1.00 \text{ E}-03$  to < 1.00 E-02 for SIL 2 safety functions. However, as the modules under consideration are only one part of an entire safety function they should not claim more than  $10\% \div 20\%$  of this range. For SIL 2 application the total PFDavg value of the SIF must be smaller than 1.00 E-02, hence the maximum allowable PFDavg value for the asset modules would then be 1.00 E-03 (for 10% contribution) and 2.00 E-03 (for 20% contribution). A similar consideration can be done for SIL 3 application, where limits are ten times smaller than correspondent limits in SIL 2 application.

The listed modules are considered to be Type A (\*) or Type B (\*\*) components, with a hardware fault tolerance of 0. According to table 2 of IEC 61508-2, for Type A components the SFF has to be:

- □ less than 60% for SIL 1 (sub-) systems with a hardware fault tolerance of 0;

- equal or more than 60% for SIL 2 (sub-) systems with a hardware fault tolerance of 0;

- □ less than 60% for SIL 2 (sub-) systems with a hardware fault tolerance of 1;

- equal or more than 90% for SIL 3 (sub-) systems with a hardware fault tolerance of 0;

- equal or more than 60% for SIL 3 (sub-) systems with a hardware fault tolerance of 1.

According to table 3 of IEC 61508-2, for Type B components the SFF has to be:

- equal or more than 60% for SIL 1 (sub-) systems with a hardware fault tolerance of 0;

- equal or more than 90% for SIL 2 (sub-) systems with a hardware fault tolerance of 0;

- equal or more than 60% for SIL 2 (sub-) systems with a hardware fault tolerance of 1;

- equal or more than 99% for SIL 3 (sub-) systems with a hardware fault tolerance of 0;

- egual or more than 90% for SIL 3 (sub-) systems with a hardware fault tolerance of 1.

If the requirements of section 11.4.4 of IEC 61511-1 First Edition 2003-01 are fulfilled, a hardware fault tolerance of 0 is sufficient for SIL 2 (sub-) systems with Type B components and having a SFF equal or more than between 60%.

Assuming that a logic solver (connected to D1000 module outputs) can detect both over-range (fail high) and under-range (fail-low), high and low failures can be classified as safe detected failures or dangerous detected failures depending on the application.

At section 5, it's showed the summary of functional safety data for each module, according to the following documents:

- □ TÜV Analysis: Compliance Certificate C IS 183645 xx and C IS 204194 xx;

- EXIDA Analysis Reports.

- (\*) Type A component: "Non-complex" component with all failure modes well defined (for details see 7.4.3.1.2 of IEC 61508-2).

- (\*\*) Type B component: "Complex" component, using micro controller (for details see 7.4.3.1.3 of IEC 61508-2).

# 2 Functional Safety Specifications from EXIDA and TÜV analysis, report according IEC 61508 - IEC 61511

Table 2: Functional Safety Specifications

| Model<br>Number                                                   | Safety Function                                     | SFF   | PFDavg<br>per year | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(10% of total<br>safety func.) | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(20% of total<br>safety func.) | Hardware Fault<br>Tolerance | EXIDA or TÜV<br>analysis | Fail-Safe<br>Output State | λSU<br>(FIT) | λDD<br>(FIT) | λDU<br>(FIT) | MTBF<br>(years) |

|-------------------------------------------------------------------|-----------------------------------------------------|-------|--------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|--------------------------|---------------------------|--------------|--------------|--------------|-----------------|

| D1010S<br>1 Ch. Active                                            | Isolating Repeater<br>Power Supply                  | 91.9% | 1.33 E-04          | TI = 7 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | ΤÜV                      | <4 mA<br>>20 mA           | 202          | 142          | 30.5         | 261             |

| D1010S<br>1 Ch. Passive                                           | Isolating Repeater<br>Power Supply                  | 91.9% | 1.49 E-04          | TI = 5 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | ΤÜV                      | <4 mA<br>>20 mA           | 229          | 157          | 34.1         | 261             |

| D1010D<br>2 Ch. Active                                            | Isolating Repeater<br>Power Supply                  | 92.0% | 1.34 E-04          | TI = 7 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | TÜV                      | <4 mA<br>>20 mA           | 207          | 146          | 30.7         | 143             |

| D1010D<br>2 Ch. Passive                                           | Isolating Repeater<br>Power Supply                  | 92.0% | 1.50 E-04          | TI = 5 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | ΤÜV                      | <4 mA<br>>20 mA           | 234          | 161          | 34.2         | 143             |

| D1010S-054<br>1 Ch.                                               | mV / mA Signal<br>Converter                         | 90.1% | 1.58 E-04          | TI = 5 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | TÜV                      | <4 mA<br>>20 mA           | 197          | 131          | 36.2         | 308             |

| D1010S-056<br>1 Ch.                                               | mV / mA Signal<br>Converter                         | 90.1% | 1.58 E-04          | TI = 5 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | ΤÜV                      | <4 mA<br>>20 mA           | 197          | 131          | 36.0         | 308             |

| D1010S-057<br>1 Ch.                                               | mV / mA Signal<br>Converter                         | 90.1% | 1.58 E-04          | TI = 5 SIL 2                                                                          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | ΤÜV                      | <4 mA<br>>20 mA           | 197          | 131          | 36.2         | 308             |

| D1014S<br>1 Ch.                                                   | Isolating Repeater<br>Power Supply                  | 93.5% | 9.91 E-05          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | TI = 2 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | ΤÜV                      | <4 mA<br>>20 mA           | 166          | 158          | 22.6         | 315             |

| D1014D<br>2 Ch.                                                   | Isolating Repeater Power Supply                     | 93.5% | 9.91 E-05          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | TI = 2 SIL 3<br>TI = 10 SIL 2                                                         | 0 - 1                       | ΤÜV                      | <4 mA<br>>20 mA           | 166          | 158          | 22.6         | 315             |

| D1020S<br>1 Ch.                                                   | Powered Isolating<br>Valve Driver                   | 82.1% | 3.08 E-04          | TI = 3 SIL 2                                                                          | TI = 6 SIL 2                                                                          | 0                           | ΤÜV                      | <4 mA                     | 323          | 0            | 70.3         | 282             |

| D1020D<br>2 Ch.                                                   | Powered Isolating<br>Valve Driver                   | 82.1% | 3.08 E-04          | TI = 3 SIL 2                                                                          | TI = 6 SIL 2                                                                          | 0 - 1                       | ΤÜV                      | <4 mA                     | 323          | 0            | 70.3         | 282             |

| D1021S<br>1 Ch.                                                   | Powered Isolating Valve Driver (F.D.)               | 70.7% | 5.18 E-04          | TI = 1 SIL 2                                                                          | TI = 3 SIL 2                                                                          | 0                           | Exida                    | <4 mA                     | 285          | 0            | 118          | 216             |

| D1032D<br>2 Ch.                                                   | Switch-Proximity Detector Repeat Relay output       | 81.3% | 2.65 E-04          | TI = 3 SIL 2                                                                          | TI = 7 SIL 2                                                                          | 0                           | TÜV                      | de-<br>energized          | 264          | 0            | 60.5         | 232             |

| D1032Q<br>4 Ch.                                                   | Switch-Proximity Detector Repeat Relay output       | 82.2% | 2.65 E-04          | TI = 3 SIL 2                                                                          | TI = 7 SIL 2                                                                          | 0                           | TÜV                      | de-<br>energized          | 280          | 0            | 60.4         | 173             |

| D1033D<br>2 Ch.                                                   | Switch-Proximity Detector Repeat O.C. Trans. output | 85.8% | 1.63 E-04          | TI = 5 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | TÜV                      | de-<br>energized          | 224          | 0            | 37.2         | 243             |

| D1033Q<br>4 Ch.                                                   | Switch-Proximity Detector Repeat O.C. Trans. output | 86.6% | 1.63 E-04          | TI = 5 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | TÜV                      | de-<br>energized          | 240          | 0            | 37.1         | 179             |

| D1034S<br>1 Ch.                                                   | Switch-Proximity<br>Detector Interface<br>mA output | 93.2% | 8.41 E-05          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | TI = 2 SIL 3<br>TI = 10 SIL 2                                                         | 0                           | TÜV                      | <1.2 mA<br>>7 mA          | 147          | 118          | 19.2         | 396             |

| D1034D<br>2 Ch.                                                   | Switch-Proximity<br>Detector Interface<br>mA output | 93.2% | 8.41 E-05          | TI = 1 SIL 3<br>TI = 10 SIL 2                                                         | TI = 2 SIL 3<br>TI = 10 SIL 2                                                         | 0 - 1                       | TÜV                      | <1.2 mA<br>>7 mA          | 147          | 118          | 19.2         | 396             |

| D1040Q<br>D1042Q<br>D1043Q<br>PSD1001(C)<br>4 Ch. Bus<br>Powered  | Isolating Solenoid<br>Valve Driver<br>for NE loads  | 80.1% | 3.64 E-04          | TI = 2 SIL 2                                                                          | TI = 5 SIL 2                                                                          | 0                           | Exida                    | de-<br>energized          | 334          | 1            | 83.0         | 248             |

| D1040Q<br>D1042Q<br>D1043Q<br>PSD1001(C)<br>4 Ch. Loop<br>Powered | Isolating Solenoid<br>Valve Driver<br>for NE loads  | 100%  | 0.00 E-00          | Lifetime = 10<br>SIL 3                                                                | Lifetime = 10<br>SIL 3                                                                | 0                           | Exida                    | de-<br>energized          | 418          | 0            | 0            | 248             |

| Model<br>Number                                                                | Safety Function                                            | SFF   | PFDavg<br>per year | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(10% of total<br>safety func.) | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(20% of total<br>safety func.) | Hardware Fault<br>Tolerance | EXIDA or TÜV<br>analysis | Fail-Safe<br>Output State                                                                                                                       | λSU<br>(FIT) | λDD<br>(FIT) | λDU<br>(FIT) | MTBF<br>(years) |

|--------------------------------------------------------------------------------|------------------------------------------------------------|-------|--------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|-----------------|

| D1044S<br>1 Ch. Bus<br>Powered,<br>NE or ND<br>loads                           | Digital Relay<br>Output                                    | 85.9% | 1.66 E-04          | TI = 6 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | ΤÜV                      | relay de-<br>energized<br>with NO<br>contact<br>(for NE<br>load) or<br>with NC<br>contact<br>(for ND<br>load)                                   | 232          | 0            | 38.0         | 420             |

| D1044S<br>1 Ch. Loop<br>Powered,<br>NE or ND<br>loads                          | Digital Relay<br>Output                                    | 88.1% | 1.40 E-04          | TI = 7 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | ΤÜV                      | relay de-<br>energized<br>with NO<br>contact<br>(for NE<br>load) or<br>with NC<br>contact<br>(for ND<br>load)                                   | 238          | 0            | 32.0         | 420             |

| D1044D<br>2 Ch.<br>Independent<br>Bus Powered<br>NE or ND<br>loads             | Digital Relay<br>Output                                    | 86.7% | 1.66 E-04          | TI = 6 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | TÜV                      | relay de-<br>energized<br>with NO<br>contact<br>(for NE<br>load) or<br>with NC<br>contact<br>(for ND<br>load)                                   | 247          | 0            | 38.0         | 241             |

| D1044D<br>1002 channel<br>architecture<br>Bus Powered<br>NE or ND<br>loads     | Digital Relay<br>Output                                    | 99.6% | 8.32 E-06          | TI = 10 SIL 3                                                                         | TI = 10 SIL 3                                                                         | 0                           | TÜV                      | relay de-<br>energized<br>with 2 NO<br>contacts<br>in series<br>(for NE<br>load) or<br>with 2 NC<br>contacts<br>in parallel<br>(for ND<br>load) | 468          | 0            | 1.9          | 241             |

| D1044D<br>1002 channel<br>architecture<br>Loop<br>Powered<br>NE or ND<br>loads | Digital Relay<br>Output                                    | 99.7% | 7.01 E-06          | TI = 10 SIL 3                                                                         | TI = 10 SIL 3                                                                         | 0                           | TÜV                      | relay de-<br>energized<br>with 2 NO<br>contacts<br>in series<br>(for NE<br>load) or<br>with 2 NC<br>contacts<br>in parallel<br>(for ND<br>load) | 468          | 0            | 1.6          | 241             |

| D1048S<br>1 Ch. Loop<br>Powered                                                | Digital Output<br>Driver for<br>NE loads                   | 100%  | 0.00 E-00          | Lifetime = 20<br>SIL 3                                                                | Lifetime = 20<br>SIL 3                                                                | 0                           | TÜV                      | de-<br>energized                                                                                                                                | 358          | 0            | 0            | 291             |

| D1049S<br>1 Ch. Bus<br>Powered                                                 | Digital Output<br>Driver for<br>NE loads                   | 99.6% | 8.32 E-06          | TI = 12 SIL 3                                                                         | TI = 20 SIL 3                                                                         | 0                           | TÜV                      | de-<br>energized                                                                                                                                | 442          | 0            | 1.9          | 240             |

| D1053S<br>Analog<br>Output                                                     | Isolating Analog<br>Signals Converter<br>& Trip Amplifiers | 80.9% | 4.16 E-04          | TI = 2 SIL 2                                                                          | TI = 4 SIL 2                                                                          | 0                           | Exida                    | <4 mA<br>>20 mA                                                                                                                                 | 135          | 267          | 95.0         | 208             |

| D1053S<br>(*) 2 Relay<br>Outputs<br>in Series                                  | Isolating Analog<br>Signals Converter<br>& Trip Amplifiers | 82.3% | 4.11 E-04          | TI = 2 SIL 2                                                                          | TI = 4 SIL 2                                                                          | 0                           | Exida                    | de-<br>energized                                                                                                                                | 437          | 0            | 94.0         | 164             |

<sup>(\*)</sup> Trip amplifier safety function concerns only the alarm with 2 relay outputs in series (terminal blocks 5-8). The analog output is not part of the safety function. Alarm A and Alarm B must be programmed with the same values.

| Model<br>Number                                              | Safety Function                                          | SFF   | PFDavg<br>per year | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(10% of total<br>safety func.) | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(20% of total<br>safety func.) | Hardware Fault<br>Tolerance | EXIDA or TÜV<br>analysis | Fail-Safe<br>Output State                    | λSU<br>(FIT) | λDD<br>(FIT) | λDU<br>(FIT) | MTBF<br>(years) |

|--------------------------------------------------------------|----------------------------------------------------------|-------|--------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|--------------------------|----------------------------------------------|--------------|--------------|--------------|-----------------|

| D1054S<br>Active IN,<br>Analog OUT                           | Isolating Repeater<br>Power Supply                       | 89.9% | 1.99 E-04          | TI = 5 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | TÜV                      | <4 mA<br>>20 mA                              | 174          | 230          | 45.5         | 197             |

| D1054S<br>Passive IN,<br>Analog OUT                          | Isolating Repeater<br>Power Supply                       | 90.5% | 2.10 E-04          | TI = 4 SIL 2                                                                          | TI = 8 SIL 2                                                                          | 0                           | TÜV                      | <4 mA<br>>20 mA                              | 194          | 261          | 48.0         | 197             |

| D1054S<br>Active IN,<br>(*) 2 Relay<br>Outputs<br>in Series  | Isolating Repeater<br>Power Supply<br>& Trip Amplifiers  | 93.1% | 1.47 E-04          | TI = 6 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | TÜV                      | de-<br>energized                             | 454          | 0            | 33.5         | 160             |

| D1054S<br>Passive IN,<br>(*) 2 Relay<br>Outputs<br>in Series | Isolating Repeater<br>Power Supply<br>& Trip Amplifiers  | 93.7% | 1.57 E-04          | TI = 6 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 0                           | TÜV                      | de-<br>energized                             | 530          | 0            | 35.9         | 160             |

| D1072S<br>1 Ch. Analog<br>Output                             | Isolating<br>Temperature<br>Signal Converter             | 83.9% | 3.33 E-04          | TI = 3 SIL 2                                                                          | TI = 6 SIL 2                                                                          | 0                           | TÜV                      | <4 mA<br>>20 mA                              | 154          | 242          | 76.0         | 226             |

| D1072D<br>2 Ch. Analog<br>Output                             | Isolating<br>Temperature<br>Signal Converter             | 86.1% | 3.71 E-04          | TI = 2 SIL 2                                                                          | TI = 4 SIL 2                                                                          | 0                           | TÜV                      | <4 mA<br>>20 mA                              | 248          | 274          | 84.7         | 151             |

| D1073S<br>Analog<br>Output                                   | Isolating Temperature Signal Converter & Trip Amplifiers | 83.9% | 3.33 E-04          | TI = 3 SIL 2                                                                          | TI = 6 SIL 2                                                                          | 0                           | TÜV                      | <4 mA<br>>20 mA                              | 154          | 242          | 76.0         | 197             |

| D1073S<br>(*) 2 Relay<br>Outputs<br>in Series                | Isolating Temperature Signal Converter & Trip Amplifiers | 88.7% | 2.85 E-04          | TI = 3 SIL 2                                                                          | TI = 6 SIL 2                                                                          | 0                           | TÜV                      | de-<br>energized                             | 509          | 0            | 65.1         | 158             |

| D1092S<br>1 Ch.<br>NE Loads                                  | Relay Output<br>module                                   | 99.1% | 7.01 E-06          | TI = 10 SIL 3<br>TI = 20 SIL 2                                                        | TI = 20 SIL 3                                                                         | 0                           | TÜV                      | de-<br>energized                             | 185          | 0            | 1.60         | 611             |

| D1092S<br>1 Ch.<br>ND Loads                                  | Relay Output<br>module                                   | 98.0% | 1.14 E-05          | TI = 7 SIL 3<br>TI = 20 SIL 2                                                         | TI = 15 SIL 3<br>TI = 20 SIL 2                                                        | 0                           | TÜV                      | energized                                    | 124          | 0            | 2.61         | 898             |

| D1092D<br>2 Ch.<br>NE Loads                                  | Relay Output<br>module                                   | 99.1% | 7.01 E-06          | TI = 10 SIL 3<br>TI = 20 SIL 2                                                        | TI = 20 SIL 3                                                                         | 0 - 1                       | TÜV                      | de-<br>energized                             | 185          | 0            | 1.60         | 611             |

| D1092D<br>2 Ch.<br>ND Loads                                  | Relay Output<br>module                                   | 98.0% | 1.14 E-05          | TI = 7 SIL 3<br>TI = 20 SIL 2                                                         | TI = 15 SIL 3<br>TI = 20 SIL 2                                                        | 0 - 1                       | TÜV                      | energized                                    | 124          | 0            | 2.61         | 898             |

| D1092S-069<br>1 Ch.<br>NO contact<br>output                  | NE Relay Output<br>module                                | 99.1% | 7.01 E-06          | TI = 10 SIL 3<br>TI = 20 SIL 2                                                        | TI = 20 SIL 3                                                                         | 0                           | TÜV                      | relay de-<br>energized<br>with NO<br>contact | 182          | 0            | 1.60         | 621             |

| D1092S-069<br>1 Ch.<br>NC contact<br>output                  | NE Relay Output<br>module                                | 99.1% | 7.01 E-06          | TI = 10 SIL 3<br>TI = 20 SIL 2                                                        | TI = 20 SIL 3                                                                         | 0                           | TÜV                      | relay de-<br>energized<br>with NC<br>contact | 182          | 0            | 1.60         | 621             |

| D1092D-069<br>2 Ch.<br>NO contact<br>output                  | NE Relay Output<br>module                                | 99.1% | 7.01 E-06          | TI = 10 SIL 3<br>TI = 20 SIL 2                                                        | TI = 20 SIL 3                                                                         | 0 - 1                       | TÜV                      | relay de-<br>energized<br>with NO<br>contact | 182          | 0            | 1.60         | 621             |

| D1092D-069<br>2 Ch.<br>NC contact<br>output                  | NE Relay Output<br>module                                | 99.1% | 7.01 E-06          | TI = 10 SIL 3<br>TI = 20 SIL 2                                                        | TI = 20 SIL 3                                                                         | 0 - 1                       | ΤÜV                      | relay de-<br>energized<br>with NC<br>contact | 182          | 0            | 1.60         | 621             |

| /*) Tring a resulti                                          |                                                          |       |                    | 1                                                                                     | l                                                                                     | 1                           |                          |                                              |              | -l <i>-</i>  |              |                 |

<sup>(\*)</sup> Trip amplifier safety function concerns only the alarm with 2 relay outputs in series (terminal blocks 5-8). The analog output is not part of the safety function. Alarm A and Alarm B must be programmed with the same values.

| Model<br>Number                                          | Safety Function                                           | SFF   | PFDavg<br>per year | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(10% of total<br>safety func.) | T Proof Test<br>(Years)<br>for defined<br>SIL value<br>(20% of total<br>safety func.) | Hardware Fault<br>Tolerance | EXIDA or TÜV<br>analysis | Fail-Safe<br>Output State | λSU<br>(FIT) | λDD<br>(FIT) | λDU<br>(FIT) | MTBF<br>(years)         |

|----------------------------------------------------------|-----------------------------------------------------------|-------|--------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|--------------------------|---------------------------|--------------|--------------|--------------|-------------------------|

| D1093S<br>1 Ch.<br>NE Loads                              | Relay Output<br>module<br>with Line & Load<br>Diagnostics | 99.2% | 7.01 E-06          | TI = 10 SIL 3                                                                         | TI = 10 SIL 3                                                                         | 0                           | ΤÜV                      | de-<br>energized          | 199          | 0            | 1.60         | 236<br>(with<br>diagn.) |

| D1093S<br>1 Ch.<br>ND Loads                              | Relay Output<br>module<br>with Line & Load<br>Diagnostics | 98.1% | 1.14 E-05          | TI = 7 SIL 3<br>TI = 10 SIL 2                                                         | TI = 10 SIL 3                                                                         | 0                           | TÜV                      | energized                 | 138          | 0            | 2.61         | 269<br>(with<br>diagn.) |

| PSD1206<br>PSD1210<br>Single Unit<br>NE Loads            | Isolated<br>Switching<br>Power Supply                     | 80.1% | 5.90 E-04          | TI = 1 SIL 2                                                                          | TI = 3 SIL 2                                                                          | 0                           | Exida                    | <2V;<br>20V<<br><30V      | 542          | 0            | 135          | 134<br>(with<br>diagn.) |

| PSD1206<br>PSD1210<br>Single Unit<br>ND Loads            | Isolated<br>Switching<br>Power Supply                     | 48.3% | 1.53 E-03          | TI = 5 SIL 1                                                                          | TI = 10 SIL 1                                                                         | 0                           | Exida                    | 20V<<br><30V              | 327          | 0            | 350          | 134<br>(with<br>diagn.) |

| PSD1206<br>PSD1210<br>2 Units<br>in parallel<br>NE Loads | Isolated<br>Switching<br>Power Supplies                   | 99.4% | 3.03 E-05          | TI = 3 SIL 3<br>TI = 10 SIL 2                                                         | TI = 6 SIL 3<br>TI = 10 SIL 2                                                         | 1                           | Exida                    | <2V;<br>20V<<br><30V      | 1084         | 0            | 6.9          | 79<br>(with<br>diagn.)  |

| PSD1206<br>PSD1210<br>2 Units<br>in parallel<br>ND Loads | Isolated<br>Switching<br>Power Supplies                   | 97.2% | 8.09 E-05          | TI = 9 SIL 2                                                                          | TI = 10 SIL 2                                                                         | 1                           | Exida                    | 20V<<br><30V              | 654          | 0            | 18.5         | 112<br>(with<br>diagn.) |

### 3 Definitions

### 3.1 Failure categories

In order to judge the failure behavior of the considered modules (except for PSD1206 and PSD1210, explained in detail at sub-section 3.1.1), the following definitions for the failure of the product must be considered:

#### □ Fail-Safe State:

Fail-safe state is defined as the output reaching the user defined threshold or as output being (de-)energized.

#### □ Fail Safe

Failure mode that causes the module/(sub)system to go to the defined fail-safe state without a demand from the process.

#### □ Fail Dangerous:

Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state).

#### □ Fail Dangerous Undetected:

Failure mode that is dangerous and that is not detected by internal diagnostics.

#### □ Fail Dangerous Detected

Failure mode that is dangerous but that is detected by internal diagnostics (these failures may be converted to the selected fail-safe state).

- ☐ Fail High: Failure mode that causes the output signal to go to the maximum limit output value.

- Fail Low: Failure mode that causes the output signal to go to the minimum limit output value.

- □ Fail "No Effect":

Failure mode of a component that is part of the safety function but has no effect on the safety function. For the calculation of SFF it is treated like a safe undetected failure.

#### Fail "Annunciation Undetected":

Failure mode that does not directly impact safety but does impact the ability to detect a future fault (such as a fault in a diagnostic circuit) and that is not detected by internal diagnostics.

For the calculation of SFF it is treated like a safe undetected failure.

#### □ Fail "Not part":

Failure mode of a component which is not part of the safety function but part of the circuit diagram and is listed for completeness. When calculating the SFF this failure mode is not taken into account. It is also not considered for the total failure rate evaluation.

Note: The "No Effect" and the "Annunciation Undetected" failures are provided for those who wish to do reliability modeling more detailed than required by IEC 61508. In IEC 61508 the "No Effect" and "Annunciation Undetected" failures are defined as safe undetected failures even though they will not cause the safety function to go to a safe state. Therefore they need to be considered in the Safe Failure Functional calculation.

# □ Fail-Safe State for: D1010, D1014; D1053S, D1054S, D1072, D1073S (using analog output)

Depending on the application, the fail-safe state is defined as the current output going to a fail low or fail high. For D1053S, D1054S, D1072 and D1073S, these low and high levels can be programmed from the user, and in this functional safety analysis they are set to 20 mA for high and 4 mA for low.

#### □ Fail-Safe State for: D1020, D1021S

The fail-safe state is defined as the output going to fail low.

# □ Fail-Safe State for: D1032, D1033 ; PSD1001(C), D1040, D1042, D1043, D1048S, D1049S (in loop/bus powered mode) ; D1053S, D1054S, D1073S (using 2 relay outputs in series)

The fail-safe state is defined as the output being de-energized or relay contacts remaining open. For D1053S, D1054S and D1073S the user can program the trip point value at which relay output must be de-energized.

#### □ Fail-Safe State for D1034

The fail-safe state is defined as the output being below 1.2 mA or above 7 mA.

#### □ Fail-Safe State for: D1044

The fail-safe state is defined as the output relay being de-energized, so that: the NO-COM contact is open and the NC-COM contact is closed.

#### □ Fail-Safe State for: D1092, D1093S

The fail-safe state is defined as:

- the output being de-energized for Normally Energized (NE) loads; or

- the output being energized for Normally De-energized (ND) loads.

#### □ Fail-Safe State for: D1092-069

The fail-safe state is defined as the relay being de-energized, so that:

- the SPST-NO contact remains open; and

- the SPST-NC contact remains closed.

- Fail Dangerous for: D1010, D1014; D1020, D1021S; D1053S, D1054S, D1072, D1073S (using analog out) Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state) or deviates the output current by more than:

- 5 % of full span (> ± 0.8 mA), for D1010, D1014, D1020, D1021S and D1054S;

- 3 % of full span (> ± 0.6 mA), for D1053S, D1072 and D1073S.

# □ Fail Dangerous for: D1032, D1033 ; PSD1001(C), D1040, D1042, D1043, D1049S (in loop/bus powered mode) ; D1053S, D1054S, D1073S (using 2 relay outputs in series)

Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state), so that the output remains energized or the relay contacts remain closed. For D1053S, D1054S and D1073S this failure leads to a measurement error of more than 3 % (of full span for D1053S and D1073S) or 5 % (of full span for D1054S) respect to the correct value and therefore the relay contacts remains closed (they don't respond to a process demand).

#### □ Fail Dangerous for D1034

Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state) or the output current remains between 1.2 mA and 7 mA.

#### □ Fail Dangerous for D1044

Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state) so that the output relay remains energized, keeping the NO-COM contact closed and the NC-COM contact open.

### □ Fail Dangerous for: D1092, D1093S

Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state) so that the output remains:

- energized for Normally Energized (NE) loads; or

- de-energized for Normally De-energized (ND) loads.

#### □ Fail Dangerous for: D1092-069

Failure mode that does not respond to a demand from the process (i.e. being unable to go to the defined fail-safe state) so that the relay remains energized, keeping the SPST-NO contact closed and the SPST-NC contact open.

□ Fail High for: D1010, D1014; D1020, D1021S; D1053S, D1054S, D1072, D1073S (using analog output) Failure mode that causes the output signal to go above the maximum output current (i.e. > 20 mA, which has been choosen in the functional safety analysis as programmed value for D1053S, D1054S, D1072 and D1073S).

#### □ Fail High for D1034

Failure mode that causes the output signal to go above 7 mA (short circuit).

□ Fail Low for: D1010, D1014; D1020, D1021S; D1053S, D1054S, D1072, D1073S (using analog output) Failure mode that causes the output signal to go below the minimum output current (i.e. < 4 mA, which has been choosen in the functional safety analysis as programmed value for D1053S, D1054S, D1072 and D1073S).

#### □ Fail Low for D1034

Failure mode that causes the output signal to go below 0.35 mA (lead breakage).

- □ Fail "No Effect" for: D1010, D1014; D1020, D1021S; D1053S, D1054S, D1072, D1073S (using analog out) Failure of a component that is part of the safety function but that has no effect on the safety function or deviates the output current by not more than:

- $\bullet$  5 % of full span (<  $\pm$  0.8 mA) for D1010, D1014, D1020, D1021S and D1054S;

- 3 % of full span (< ± 0.6 mA) for D1053S, D1072 and D1073S.

For the calculation of SFF it is treated like a safe undetected failure.

### 3.1.1 Failure categories for PSD1206 and PSD1210

In order to judge the failure behavior of the PSD1206 and PSD1210, the following definitions for the failure of the product must be considered:

- □ Fail-Safe State: The fail-safe state is defined as the output reaching the user defined threshold. In normally energized (NE) loads, is defined as the output being between 20 V and 30 V (load current up to 80% of rated) or lower than 2V. In normally de-energized (ND) loads, is defined as the output being between 20 V and 30 V (load current up to 80% of rated).

- Fail Safe: Failure that causes the output to go to the defined fail-safe state without a demand from the process.

- □ Fail Dangerous:

- With normally energized (NE) loads, failure that leads to an output higher than 30 V or between 2 V and 20 V. With normally de-energized (ND) loads, failure that leads to an output higher than 30 V or lower than 20 V.

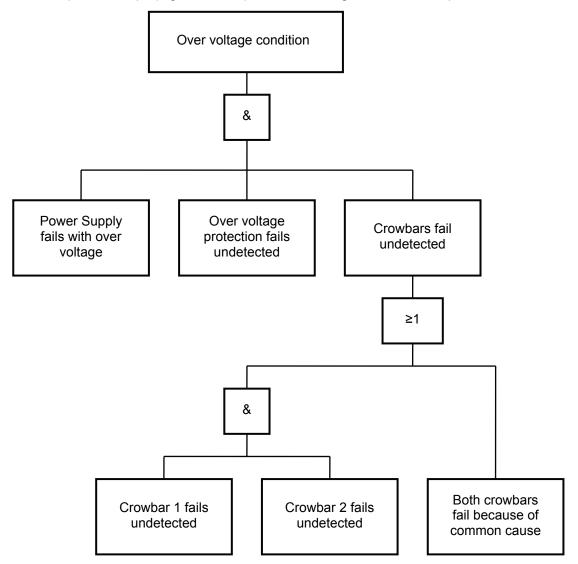

- □ Fail High: Failure mode that leads to an over voltage condition (> 30 V).

- Fail Low: Failure mode that leads to an under voltage condition (< 2 V).</p>

- □ Fail "No Effect": Failure mode of a component that is part of the safety function but has no effect on the safety function. For the calculation of SFF it is treated like a safe undetected failure.

- Fail "Annunciation Undetected": Failure mode that does not directly impact safety but does impact the ability to detect a future fault (such as a fault in a diagnostic circuit) and that is not detected by internal diagnostics. For the calculation of SFF it is treated to 1 % as a dangerous failure and to 99 % as a no effect failure as in this system there are 3 different over voltage protection mechanism.

- □ **Fail "Not part":** Failures of a component which is not part of the safety function but part of the circuit diagram and is listed for completeness. When calculating the SFF this failure mode is not taken into account. It is also not considered for the total failure rate evaluation.

### 3.2 General Terms

- **DC:** Diagnostic coverage (safe or dangerous) of the safety logic solver for the considered module.

- **DCs:** Diagnostic coverage for safe failures =  $\lambda$ sd / ( $\lambda$ sd +  $\lambda$ su).

- **DCd:** Diagnostic coverage for dangerous failures =  $\lambda$ dd / ( $\lambda$ dd +  $\lambda$ du).

- □ **FIT:** Failure In Time (1x10 E-9 failures per hour).

#### □ Failure Rates:

The failure rate data used in the FMEDA analysis are the basic failure rates from the Siemens SN 29500 failure rate database. The rates where chosen in a way that is appropriate for safety integrity level verification calculations, and to mach operating stress conditions typical of an industrial field environment similar to IEC 60654-1, class C. It is expected that the actual number of field failures will be less than the number predicted by these failure rates.

#### □ FMEA:

Failure Modes and Effects Analysis is a systematic way to identify and evaluate the effects of different component failure modes, to determine what could eliminate or reduce the chance of failure, and to document the system in consideration.

#### □ FMEDA:

Failure Modes Effects and Diagnostic Analysis is an FMEA extension. It combines standard FMEA techniques with extension to identify online diagnostics techniques and the failure mode relevant to safety instrumented system design. It is a technique recommended to generate failure rates for each important category (safe detected, safe undetected, dangerous detected, dangerous undetected, fail high, fail low) in the safety modules. The format for the FMEDA is an extension of the FMEA format MIL STD 1629A.

#### □ Low demand mode:

Mode where the frequency of demands for operation made on Safety-related system is no greater than one per year and no greater than twice the proof test frequency.

- □ MTBF: Mean Time Between Failure.

- MTTF: Mean Time To Failure.

- □ MTTF<sub>s</sub>: Mean Time To safe Failure.

- MTTF<sub>D</sub>: Mean Time To dangerous Failure.

- MTTR: Mean Time To Repair.

- □ **PFDavg:** Average Probability of Failure on Demand.

- □ SFF:

Safe Failure Fraction, according IEC 61508 summarizes the fraction of failures, which lead to a safe state and the fraction of failures which will be detected by diagnostic measures and lead to a defined safety action.

$$SFF = \frac{\lambda DD + \lambda SD + \lambda SU}{\lambda DD + \lambda DU + \lambda SD + \lambda SU} = 1 - \frac{\lambda DU}{\lambda DD + \lambda DU + \lambda SD + \lambda SU}$$

with: λDD: Dangerous Detected failure rate; λDU: Dangerous Undetected failure rate

λSD: Safe Detected failure rate; λSU: Safe Undetected failure rate

- □ SIF: Safety Instrumented Function.

- □ SIS: Safety Instrumented System.

- SIL: Safety Integrity Level.

#### □ T Proof Test & Maintenance (TI) :

Proof Test Interval (for example 1 - 5 - 10 years, with 1 year = 8760 hours).

Maintenance time is considered 8 hours.

# 4 Assumptions

The following assumptions have been made during the Failure Modes, Effects, and Diagnostic Analysis of the Repeater/Driver/Interface/Converter/Relay Modules D1010, D1014, D1020, D1021S, D1032, D1033, D1034, D1040, D1042, D1043, D1044, D1048S, D1049S, D1053S, D1054S, D1072, D1073S, D1092, D1092-069, D1093S and PSD1001(C) power supply.

- □ Failure rates are constant, wear out mechanisms are not included. Propagation of failures is not relevant.

- □ Failures during parameterization are not considered.

- ☐ The HART protocol is only used for setup, calibration, and diagnostic purposes, not for safety critical operation.

- The time to restoration or repair time after a safe failure is 8 hours, as MTTR.

- All modules are operated in the low demand mode of operation.

- External power supply failure rates are not included.

- □ The stress levels are average for an industrial environment and can be compared to the Ground Fixed classification of MIL-HNBK-217F. Alternatively, the assumed environment is similar to IEC 654-1, Class C (sheltered location) with temperature limits within the manufacturer's rating and an average temperature over a long period of time of 40 °C. Humidity levels are assumed within manufacturer's rating.

- The listed failure rates are valid for operating stress conditions typical of an industrial field environment similar to IEC 60654-1 class C with an average temperature over a long period of time of 40°C. For a higher average temperature of 60 °C, the failure rates should be multiplied with an experience based factor of 2.5. A similar multiplier should be used if frequent temperature fluctuation must be assumed.

- Only one input and one output are part of the safety function.

- □ For D1010, D1014 and D1053S, D1054S, D1072, D1073S (using analog output) modules, only the current output is used for safety applications.

- For D1053S, D1054S and D1073S (using 2 relay outputs in series) modules, the trip amplifier safety function concerns only the alarm with 2 relay outputs in series (terminal blocks 5-8). Therefore the analog output is not part of this safety function. In addition, the common cause factor (β) for the 2 relays in series is considered to be 5 %. Then, the 2 relay outputs connected in series can be protected by appropriate mean (e.g. a fuse) which initiates at 60% of the rated current to avoid contact welding.

- □ For D1032 D1033 modules, only the 2<sup>nd</sup> actuation mode configuration (NO input → ND relay or NO transistor output (or its equivalent NC input → NE relay or NC transistor output)) can be used for safety application. Then, input line short open fault detection has been enabled to de-energized output relay transistor in case of fault.

- □ For D1049S module, only the 1<sup>st</sup> operating mode (direct In/Out transfer function: "input high or 24 Vdc → output is energized" or its equivalent "input low or 0 Vdc → output is de-energized") can be used for safety application. For both D1048S and D1049S modules, the override functionality has been disabled, so that the Safety PLC or DCS driving/control signal is the only signal that operates on the channel. In addition, the line and load fault (output short or open circuit) detection has been enabled to de-energized the load in case of fault, until normal condition is restored.

- □ The application program in the safety logic solver is configured in such a way that fail low (under-range failure) and fail high (over-range failure) are detected regardless of the effect, safe or dangerous, on the safety function.

- The 4-20 mA output signal is fed to a SIL 2 SIL 3 compliant analog input board of a safety PLC.

- Sufficient test are performed prior to shipment to verify the absence of vendor and/or manufacturing defects, that prevent proper operation of specified functionality to product specifications or cause operation different from design analyzed.

- □ Safety Integrity Levels as defined in IEC 61508 and IEC 61511:

| SIL<br>Safety Integrity Level | PFDavg Average probability of failure on demand per year (low demand) | RRF<br>Risk Reduction<br>Factor | PFDavg Average probability of dangerous failure on demand per hour (high demand) |

|-------------------------------|-----------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|

| SIL 4                         | $\geq 10^{-5} \text{ to} < 10^{-4}$                                   | from 100000 to 10000            | $\geq 10^{-9} \text{ to} < 10^{-8}$                                              |

| SIL 3                         | $\geq 10^{-4} \text{ to} < 10^{-3}$                                   | from 10000 to 1000              | $\geq 10^{-8} \text{ to} < 10^{-7}$                                              |

| SIL 2                         | $\geq 10^{-3} \text{ to} < 10^{-2}$                                   | From 1000 to 100                | $\geq 10^{-7} \text{ to} < 10^{-6}$                                              |

| SIL 1                         | $\geq 10^{-2} \text{ to} < 10^{-1}$                                   | From 100 to 10                  | $\geq 10^{-6} \text{ to} < 10^{-5}$                                              |

### 4.1 Assumption for PSD1206 and PSD1210

The following assumptions have been made during the Failure Modes, Effects, and Diagnostic Analysis of the Switching Power Supply Types PSD1206 and PSD1210.

- □ Failure rates are constant, wear out mechanisms are not included.

- Propagation of failures is not relevant.

- Failures during parameterization are not considered.

- Sufficient test are performed prior to shipment to verify the absence of vendor and/or manufacturing defects that prevent proper operation of specified functionality to product specifications or cause operation different from design analyzed.

- ☐ The device is operated in the low demand mode of operation.

- ☐ The time to restoration or repair time after a safe failure is 8 hours, as MTTR.

- Only the described versions are used for safety applications.

- Practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDAs.

- □ The fault output is not part of the safety function.

- $\Box$  The common cause factor  $\beta$  between the two crowbars is estimated at be 5 %.

- □ The stress levels are average for an industrial environment and the assumed environment is similar to IEC 60654-1, Class C (Sheltered location) with temperature limits within the manufacturer's rating and an average temperature over a long period of time of 40 °C.

Humidity levels are assumed within manufacturer's rating.

- □ The listed failure rates are valid for operating stress conditions typical of an industrial field environment similar to IEC 60654-1 class C with an average temperature over a long period of time of 40 °C. For a higher average temperature of 60 °C, the failure rates should be multiplied with an experience based factor of 2.5. A similar multiplier should be used if frequent temperature fluctuation must be assumed.

- Over-voltage protection has a diagnostic coverage of 99 %.

# 5 Summary of Data from EXIDA and TÜV analysis

Note:

in the following "PFDavg vs T[Proof]" tables with determination of SIL, green color indicates that PFDavg of the unit is less than or equal to 10% or 20% of the PFDavg required by its SIL level (see table at section 4), while yellow color indicates that PFDavg of the unit is more than 10% or 20% of the PFDavg required by its SIL level.

# 5.1 D1010S Isolating Repeater Power Supply, Hart Compatible (Active Input)

In the following tables are shown functional safety data, as defined in TÜV Compliance Certificate C - IS - 183645 - xx. Table 3: Failure rates

| Failure category                                                                                             | Failure rates (FIT) |

|--------------------------------------------------------------------------------------------------------------|---------------------|

| Total Fail Dangerous Detected = λdd                                                                          | 141.58              |

| ∜ Fail Dangerous Detected (internal diagnostics or indirectly)                                               | 1.83                |

| ∜ Fail High (detected by the logic solver)                                                                   | 30.50               |

|                                                                                                              | 109.25              |

| Total Fail Dangerous Undetected = λdu                                                                        | 30.47               |

| Total Fail Safe Detected = λsd                                                                               | 0.00                |

| Total Fail Safe Undetected = λsu = Fail "No Effect"                                                          | 201.95              |

| Total Failure Rate (Safety Function) = λsd + λsu + λdd + λdu                                                 | 374.00              |

| Fail "Not Part" = λnotpart                                                                                   | 62.60               |

| Total Failure Rate (Device) = λsd + λsu + λdd + λdu + λnotpart                                               | 436.60              |

| <b>MTBF</b> = MTTF + MTTR = $1/(\lambda sd + \lambda su + \lambda dd + \lambda du + \lambda notpart) + MTTR$ | 261 years           |

| $MTTF_S = 1/(\lambda sd + \lambda su)$                                                                       | 565 years           |

| $MTTF_D = 1/\lambda du$                                                                                      | 3746 years          |

Table 4: Failure rates according to IEC 61508

| λsd      | λsu        | λdd        | λdu       | SFF    | DCs   | DCd    |

|----------|------------|------------|-----------|--------|-------|--------|

| 0.00 FIT | 201.95 FIT | 141.58 FIT | 30.47 FIT | 91.85% | 0.00% | 82.29% |

Table 5: PFDavg vs T[Proof], with determination of SIL supposing module contributes 10% of entire safety function

| T[Proof] = 1 year                            | T[Proof] = 7 years                           | T[Proof] = 10 years             |  |  |  |  |

|----------------------------------------------|----------------------------------------------|---------------------------------|--|--|--|--|

| PFDavg = 1.33 E-04<br>Valid for <b>SIL 2</b> | PFDavg = 9.34 E-04<br>Valid for <b>SIL 2</b> | PFDavg = 1.33 E-03              |  |  |  |  |

| See Note 2 Section 6                         | See Note 2 Section 6                         | See Note 3 and Note 4 Section 6 |  |  |  |  |

Table 6: PFDavg vs T[Proof], with determination of SIL supposing module contributes 20% of entire safety function

| T[Proof] = 1 year                            | T[Proof] = 10 years                          |

|----------------------------------------------|----------------------------------------------|

| PFDavg = 1.33 E-04<br>Valid for <b>SIL 3</b> | PFDavg = 1.33 E-03<br>Valid for <b>SIL 2</b> |

| See Note 6 Section 6                         | See Note 7 Section 6                         |

# 5.2 D1010S Isolating Repeater Power Supply, Hart Compatible (Passive Input)

In the following tables are shown functional safety data, as defined in TÜV Compliance Certificate C - IS - 183645 - xx. Table 7: Failure rates

| Failure category                                                                                             | Failure rates (FIT) |

|--------------------------------------------------------------------------------------------------------------|---------------------|

| Total Fail Dangerous Detected = λdd                                                                          | 157.07              |

| ∜ Fail Dangerous Detected (internal diagnostics or indirectly)                                               | 1.83                |

| ∜ Fail High (detected by the logic solver)                                                                   | 35.04               |

| ∜ Fail Low (detected by the logic solver)                                                                    | 120.20              |

| Total Fail Dangerous Undetected = λdu                                                                        | 34.08               |

| Total Fail Safe Detected = λsd                                                                               | 0.00                |

| Total Fail Safe Undetected = λsu = Fail "No Effect"                                                          | 229.05              |

| Total Failure Rate (Safety Function) = λsd + λsu + λdd + λdu                                                 | 420.20              |